@浙江 杨 资料已经上传 知识库 工艺 BCD 文件夹

高压LDMOS(横向双扩散金属氧化物半导体)是功率IC的“核心肌肉单元”,通过横向电流传输+漂移区耐压设计,实现80V-1200V高压耐受能力,同时兼顾低导通电阻(R_{on,sp)与高频特性,广泛应用于汽车电子(48V电源、电机驱动)、工业电源(AC-DC转换)、射频功率放大(5G基站)等场景。其核心价值在于解决“高压耐压”与“低导通损耗”的矛盾,通过电场、热场、载流子输运的协同优化,支撑大功率、高效率的电力转换与信号放大。

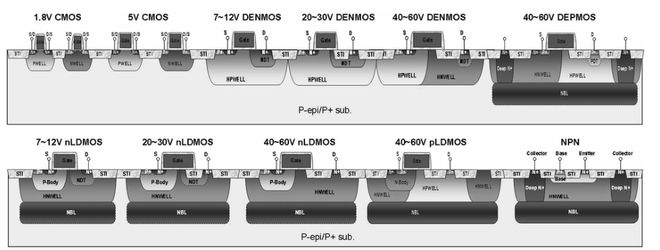

典型流程基于外延衬底+多步掺杂+隔离增强+场调控技术

①衬底与埋层制备:耐压基础

衬底选择:主流采用P⁺重掺杂衬底+P⁻轻掺杂外延层(P-epi),外延层电阻率0.5-2Ω·cm、厚度5-15μm(耐压越高,外延层越厚)。例如Dongbu HiTek的BD180工艺使用7Ω·cm的P-epi/P⁺衬底,支撑60V LDMOS;UESTC的700V BCD工艺则直接采用80-130Ω·cm的P型单晶衬底,省去外延步骤(全注入工艺),降低成本。

埋层(NBL)注入:通过Sb(锑)离子注入形成N⁺埋层(浓度1e19-5e19/cm³),用于:①垂直NPN晶体管的集电极;②高压LDMOS的隔离与电流引导。BD180工艺的NBL可有效避免高压LDMOS的穿通击穿,提升高侧器件可靠性。

②高压阱(HV Well)与漂移区掺杂:电场调控核心

HV Well形成:采用两次离子注入形成HVNWELL(N型高压阱)与HVPWELL(P型高压阱),分别对应N-ch LDMOS与P-ch LDMOS的耐压区。BD180工艺的HVNWELL设计击穿电压85V,HVPWELL达100V,通过调整注入剂量(N型:1e12-5e12/cm²,P型:5e11-2e12/cm²)与退火温度(850-950℃),实现阱区深度5-8μm,为漂移区提供“电场缓冲”。

漂移区优化:

低掺杂N⁻漂移区(浓度1e15-5e15/cm³)是耐压关键,通过RESURF(降低表面电场)技术实现电荷平衡——例如在N⁻漂移区下方注入P型埋层(浓度1e16/cm³),使横向耗尽层与纵向耗尽层匹配,避免表面电场集中。UESTC的700V LDMOS通过double RESURF技术,将漂移区表面电场均匀化至20V/μm,击穿电压提升至800V。

阶梯掺杂漂移区(Step Drift):采用多级浓度梯度(如1e16→5e15→1e15/cm³),在相同耐压下缩短漂移区长度(如从20μm减至12μm),$$R_{on,sp$$降低40%。

③双扩散(Double Diffusion):沟道精准控制

LDMOS的核心工艺创新是两次扩散突破光刻极限,实现亚微米级沟道(0.3-0.5μm):

第一次扩散(P-body):注入B(硼,浓度1e15-5e15/cm³),形成P型体区,定义沟道的“源极侧边界”;

第二次扩散(N⁺源/漏):注入P(磷,浓度1e17-1e18/cm³),形成N⁺源区与漏区,其中源区与P-body的掺杂差定义沟道长度(无需依赖光刻精度)。BD180工艺的1.8V CMOS与5V CMOS通过双扩散实现0.18μm沟道,与高压LDMOS工艺兼容。

④ 隔离与栅极工艺:抑制串扰与增强可靠性

隔离技术:

深沟槽隔离(DTI):刻蚀深度5-10μm的沟槽,填充SiO₂,实现高压LDMOS与低压CMOS的电气隔离,降低寄生电容。ST的BCD工艺中,DTI可将隔离电阻提升至1e9Ω,避免高压串扰;

场隔离环(FIR):围绕高压LDMOS的P⁺环注入,进一步抑制衬底电流,提升ESD robustness(摘要5)。

栅极与场板设计:

栅极:采用多晶硅栅(厚度150-200nm),栅氧厚度根据电压等级调整(7V LDMOS:10nm;600V LDMOS:50nm),BD180工艺的栅氧击穿电压达34V(MIM电容);

场板(Field Plate):多晶硅/金属场板延伸至漂移区(覆盖长度占漂移区30%-50%),将漏端峰值电场从3e5 V/cm降至1.5e5 V/cm,击穿电压提升20%-30%(摘要1)。英飞凌的高压LDMOS通过“多段场板+氧化层阶梯”,进一步优化电场分布。

⑤金属化与钝化:降低导通损耗与增强可靠性

金属化:采用多层金属(最多6层),顶层金属厚度2.7-5μm(如BD180工艺),降低金属线电阻;源极采用“叉指型布局”,增大电流扩展面积,减少电流拥挤效应;

钝化:采用Si₃N₄+SiO₂叠层钝化,保护栅氧与漂移区,抵抗离子迁移与湿气侵蚀,700V LDMOS的钝化层击穿电压达88V。

高压LDMOS制造核心难点

1. 高压与低压器件的工艺兼容(BCD集成场景)

BCD工艺中,高压LDMOS(80-1200V)与低压CMOS(1.8-5V)、BJT需共享流程,难点在于:

掺杂冲突:高压LDMOS的低掺杂漂移区与低压CMOS的高掺杂源漏区需避免相互污染,需通过“掩膜隔离+注入角度控制”实现。例如采用“深沟槽隔离(DTI)+电荷耦合结构”,在48V汽车BCD芯片中实现高压LDMOS与1.8V逻辑CMOS的隔离,串扰电压<50mV;

热预算矛盾:高压LDMOS的退火温度(850-950℃)可能导致低压CMOS的阈值电压漂移,需优化退火时间(30-60s)与氛围(N₂/O₂混合),BD180工艺通过“分段退火”(低温激活+高温推进),使1.8V NMOS的阈值电压漂移<0.05V。

超结(SJ-LDMOS)通过交替N柱/P柱实现电荷平衡,是600V以上高压LDMOS的主流结构,但制造难点在于:

P柱掺杂均匀性:传统SJ-LDMOS的P柱需与N柱严格匹配(电荷平衡比1:1),否则会导致电场集中。摘要4提出“部分轻掺杂P柱(PD SJ-LDMOS)”,通过P柱浓度梯度(1e15→5e14/cm³)抑制衬底辅助耗尽效应,当漂移长度15μm时,表面电场均匀性提升30%,击穿电压达300V;

深槽刻蚀精度:SJ-LDMOS的N/P柱需通过深槽刻蚀(深度5-8μm)形成,刻蚀垂直度(>89.5°)与侧壁粗糙度(<5nm)直接影响耐压,ST的MDmesh工艺通过“等离子体刻蚀+侧壁钝化”,将深槽刻蚀偏差控制在±0.1μm。

高压LDMOS工作时,漂移区与漏区易产生局部热点(结温>150℃),导致载流子迁移率下降、$$R_{on,sp$$增大,制造难点在于:

热阻降低:传统体硅LDMOS的热阻($$R_{th$$)约5-10℃/W,需集成局部SOI或DTI结构。摘要1提到,采用“DTI+SiC局部衬底”(ST的SILICARB技术),将$$R_{th$$降至1.5-3℃/W,20A连续工作时结温波动<15℃;

布局优化:漏区采用“圆形/椭圆形”设计(曲率半径>5μm),避免电流拥挤导致的局部过热,对称氧化沟槽LDMOS通过“沟槽分散电流路径”,热点温度降低25%。

高压LDMOS面临“热载流子注入(HCI)”“时间相关介质击穿(TDDB)”等可靠性问题,制造难点在于:

热载流子抑制:漏区与漂移区的掺杂梯度需平缓,避免电场集中导致的载流子加速。中ST的MDmesh工艺通过“渐变N⁺漏区(浓度1e17→5e16/cm³)”,将热载流子注入率降低40%,器件寿命提升至1e6小时;

栅氧可靠性:高压LDMOS的栅氧厚度大(50-100nm),但长期高压应力下易产生氧空位。的700V工艺通过“栅氧生长后N₂O退火”,将栅氧陷阱密度降至1e10/cm²,TDDB寿命提升至1e5小时(125℃,50%额定电压)。

海外龙头企业的高压LDMOS工艺实践

ST、英飞凌、TI等海外龙头通过“IDM模式+结构创新+工艺垂直整合”,主导高压LDMOS技术方向

1. ST(意法半导体):超结与材料创新

ST以MDmesh超结技术为核心,构建STPOWER品牌的高压LDMOS产品线,关键策略:

超结结构优化:MDmesh系列采用“深槽刻蚀N/P柱+部分轻掺杂P柱”,实现电荷平衡比1:1.05,600V LDMOS的$$R_{on,sp$$低至5mΩ·cm²,FOM($$BV²/R_{on,sp$$)达72MW/cm²;

SiC异质集成:推出SILICARB技术,在硅基LDMOS的漂移区局部嵌入SiC衬底(热导率490W/m·K,是硅的3倍),1200V LDMOS的$$R_{th$$降至1.2℃/W,适用于新能源汽车的OBC(车载充电机);

BCD全集成:将MDmesh LDMOS与CMOS、BJT集成于BCD工艺,例如汽车48V电源芯片中,集成60V LDMOS(电机驱动)、5V CMOS(逻辑控制)、BJT(过流保护),芯片面积减少30%,效率达98.5%。

英飞凌聚焦“高压+高频”场景,以COOLMOSTM超结技术与三维堆叠为核心:

超结工艺突破:COOLMOSTM采用“多步注入形成N/P柱”,避免深槽刻蚀的侧壁缺陷,1200V LDMOS的$$R_{on,sp$$低至3.2mΩ·cm²,适用于工业变频器;

射频LDMOS创新:5G基站用GaN-on-Si LDMOS,通过“GaN异质结+场板优化”,28GHz频段的PAE(功率附加效率)达65%,优于传统硅基LDMOS的50%;

三维集成(TSV):采用硅通孔(TSV)将多颗LDMOS垂直堆叠(MultiPower技术),电流密度提升3倍(达300A/cm²),适用于大功率服务器电源。

TI以Fusion BCD工艺为核心,实现高压LDMOS与低压电路的深度集成:

工艺兼容性设计:Fusion工艺支持1.8V/5V CMOS、60-120V LDMOS、EEPROM的单片集成,通过“共享HV Well+DTI隔离”,减少掩膜步骤至10步(传统工艺15步),成本降低20%;

汽车级可靠性强化:针对汽车电子,优化LDMOS的“源极叉指布局+钝化层”,ESD防护能力达8kV(HBM),工作温度范围-40℃~150℃,满足AEC-Q100 Grade 0标准;

系统级功能集成:在48V汽车DC-DC芯片中,集成120V LDMOS(功率开关)、电流采样电阻、过温保护电路,转换效率达98.8%,体积减少40%。

高压LDMOS的工艺核心是“电场调控+热管理+兼容性设计”,海外龙头通过超结结构、材料创新、IDM垂直整合构建技术壁垒;

特别声明:以上内容(如有图片或视频亦包括在内)为自媒体平台“网易号”用户上传并发布,本平台仅提供信息存储服务。

Notice: The content above (including the pictures and videos if any) is uploaded and posted by a user of NetEase Hao, which is a social media platform and only provides information storage services.

北京

北京